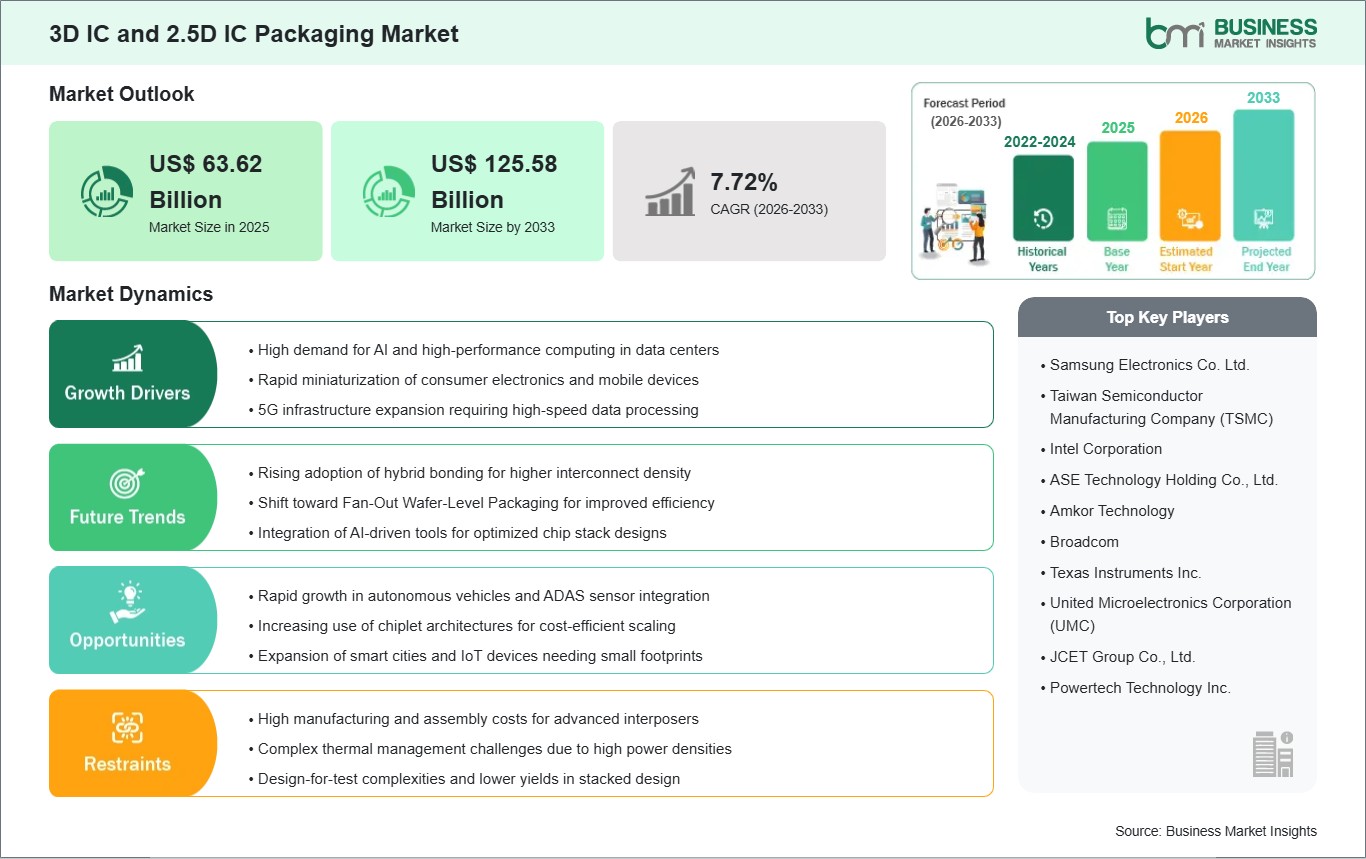

The 3D IC and 2.5D IC Packaging Market size is expected to reach US$ 125.58 Billion by 2033 from US$ 63.62 Billion in 2025. The market is estimated to record a CAGR of 8.87% from 2026 to 2033.

3D and 2.5D IC Packaging represent the vanguard of semiconductor architecture, enabling the vertical and horizontal integration of multiple silicon dies into a single high-performance unit. These technologies are critical for overcoming the physical limitations of Moore's Law, offering significantly higher interconnect density, reduced latency, and improved power efficiency compared to traditional 2D layouts. By utilizing Through-Silicon Vias (TSVs) and silicon interposers, these packaging solutions facilitate the "More than Moore" era, essential for the next generation of high-performance computing (HPC), artificial intelligence (AI), and 5G infrastructure.

However, the industry faces substantial technical and economic restraints that could impact widespread adoption. The manufacturing process is inherently complex, requiring high-precision equipment for wafer thinning and hybrid bonding, which often leads to yield management challenges and high initial capital expenditure (CapEx). Thermal management remains a critical hurdle, as stacking active dies creates localized "hot spots" that require advanced cooling solutions to prevent performance degradation. Furthermore, supply chain sensitivities, such as long lead times for specialized manufacturing tools and geopolitical export controls on advanced packaging equipment, pose ongoing risks.

Despite these challenges, the market remains characterized by lucrative opportunities, particularly as the industry transitions to chiplet-based architectures and heterogeneous integration. The surge in demand for High-Bandwidth Memory (HBM) and the expansion of sovereign semiconductor ecosystems through government incentives, such as the CHIPS Act, ensure a robust growth trajectory for players capable of mastering these high-density integration techniques.

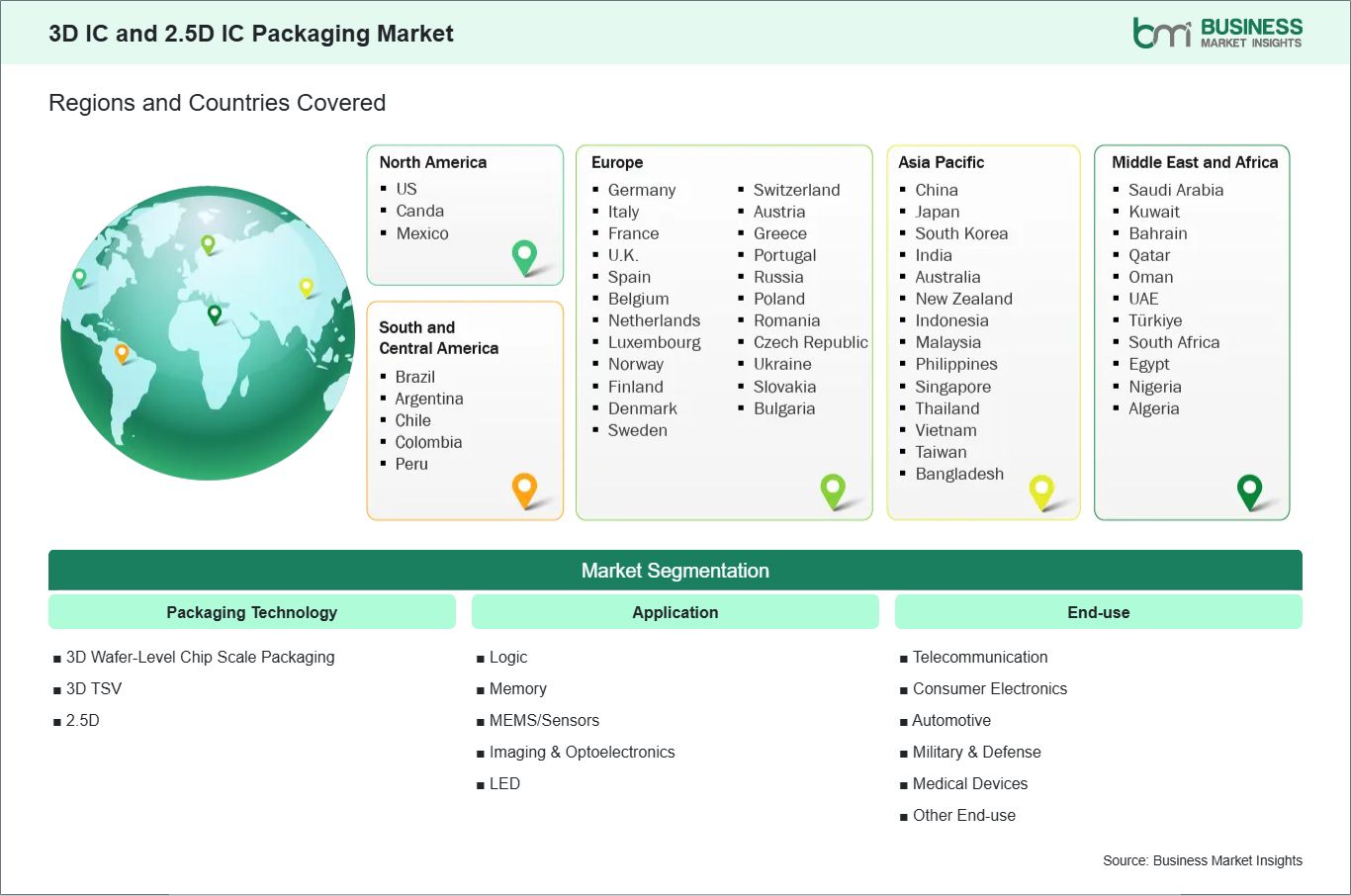

Key segments that contributed to the derivation of the 3D IC and 2.5D IC Packaging market analysis are packaging technology, application, and end-use.

The surging demand for Generative AI and High-Performance Computing (HPC) serves as the primary engine driving the 3D and 2.5D IC packaging market. Modern AI workloads, particularly those involving large language models (LLMs) like GPT-4, require massive data transfer speeds that traditional 2D architectures cannot sustain. Advanced packaging technologies, such as 2.5D interposers and 3D Through-Silicon Vias (TSVs), provide the critical vertical highway needed to couple high-performance GPUs with High-Bandwidth Memory (HBM) stacks.

By integrating memory and logic in a three-dimensional footprint, manufacturers can achieve bandwidths exceeding 1,000 GB/s, effectively breaking the "memory wall" that limits computational throughput. This vertical integration drastically shortens interconnect lengths, which not only reduces latency by several orders of magnitude but also lowers energy-per-bit consumption, a vital factor for hyperscale data centers facing rising operational costs. As compute intensity continues to double every few months, the industry is shifting its focus from transistor shrinkage (Moore's Law) toward advanced packaging as the primary lever for performance scaling. Consequently, major semiconductor firms and cloud service providers are making multi-billion-dollar capital commitments to secure advanced packaging capacity, ensuring sustained market momentum through 2033.

A transformative opportunity lies in the global transition toward chiplet-based architectures and heterogeneous integration. As the cost and complexity of manufacturing monolithic System-on-Chips (SoCs) on leading-edge nodes (3nm and beyond) become prohibitively high, the industry is moving toward a modular "LEGO-like" design philosophy. This involves disaggregating a large chip into smaller, functional "chiplets", such as logic, I/O, and memory, that can be manufactured on different, optimized process nodes and then reassembled into a single package.

This approach offers significant economic advantages, including drastically improved manufacturing yields and the ability to reuse proven IP blocks, which shortens time-to-market. The rise of standardized interconnect protocols, such as Universal Chiplet Interconnect Express (UCIe), allows for a multi-vendor ecosystem where designers can mix and match chiplets from different suppliers. This modularity is particularly lucrative for specialized sectors like Automotive ADAS, where sensor fusion and edge AI require high-density integration in compact, thermally efficient footprints. Furthermore, as the industry moves toward integrating hundreds, and eventually thousands, of chiplets into a single wafer-level system, the demand for precision bonding services and advanced redistribution layers (RDL) will create an expansive new revenue frontier for OSATs (Outsourced Semiconductor Assembly and Test) and foundries alike.

The 3D IC and 2.5D IC Packaging market demonstrates steady growth, with size and share analysis revealing evolving trends and competitive positioning among key players. The report further examines subsegments categorized within packaging technology, application, and end-use, offering insights into their contribution to overall market performance.

For instance, the 3D TSV currently holds a dominant share in the technology segment due to its essential role in AI accelerators and HBM stacks.

Within the application category, Logic continues to lead the market, representing over half of the revenue as high-end processors transition to multi-die configurations to maintain performance scaling.

From an end-use perspective, Consumer Electronics remains the most significant volume contributor, fueled by the relentless demand for miniaturization in smartphones and wearables.

| Report Attribute | Details |

|---|---|

| Market size in 2025 | US$ 63.62 Billion |

| Market Size by 2033 | US$ 125.58 Billion |

| Global CAGR (2026 - 2033) | 8.87% |

| Historical Data | 2022-2024 |

| Forecast period | 2026-2033 |

| Segments Covered | By Packaging Technology

|

|

Regions and Countries Covered

| |

| North America | US, Canada, Mexico |

| Europe | Belgium, Austria, Finland, Denmark, Greece, Poland, Romania, Russia, Ukraine, Czech Republic, Slovakia, Bulgaria, Italy, Luxembourg, Germany, Switzerland, France, Netherlands, Norway, Portugal, Spain, Sweden, United Kingdom |

| Asia-Pacific | Australia, China, India, Japan, South Korea, Indonesia, Malaysia, Philippines, Singapore, Thailand, Vietnam, Bangladesh, New Zealand, Taiwan |

| South and Central America | Brazil, Argentina, Peru, Chile, Colombia |

| Middle East and Africa | Bahrain, Kuwait, Oman, Qatar, Saudi Arabia, United Arab Emirates, Turkiye, South Africa, Egypt, Algeria, Nigeria |

| Market leaders and key company profiles |

|

The "3D IC and 2.5D IC Packaging Market Size and Forecast (2022 - 2033)" report provides a detailed analysis of the market covering below areas:

The geographical scope of the 3D IC and 2.5D IC Packaging market report is divided into five regions: North America, Asia Pacific, Europe, the Middle East &Africa, and South &Central America.

In North America, the market is characterized by a strong emphasis on the research and design of high-end AI accelerators and the expansion of domestic advanced packaging facilities to secure critical semiconductor supply chains. The Asia-Pacific region serves as a core manufacturing hub, utilizing its extensive network of foundries and outsourced semiconductor assembly and test providers to support high-volume production. Europe maintains a specialized focus on the automotive and industrial sectors, where packaging solutions are developed to meet rigorous reliability and thermal management standards for vehicle safety systems. The Middle East &Africa are witnessing steady adoption through investments in digital infrastructure and data centers, while South &Central America are seeing a gradual increase in back-end assembly and testing activities for regional consumer markets. This regional diversity ensures that as global demand for miniaturized, high-performance electronics grows, each geography leverages its local expertise to contribute to the broader market expansion.

The 3D IC and 2.5D IC Packaging market is evaluated by gathering qualitative and quantitative data post primary and secondary research, which includes important corporate publications, association data, and databases. A few of the key developments in the 3D IC and 2.5D IC Packaging market are:

The 3D IC and 2.5D IC Packaging Market is valued at US$ 63.62 Billion in 2025, it is projected to reach US$ 125.58 Billion by 2033.

As per our report 3D IC and 2.5D IC Packaging Market, the market size is valued at US$ 63.62 Billion in 2025, projecting it to reach US$ 125.58 Billion by 2033. This translates to a CAGR of approximately 8.87% during the forecast period.

The 3D IC and 2.5D IC Packaging Market report typically cover these key segments-

The historic period, base year, and forecast period can vary slightly depending on the specific market research report. However, for the 3D IC and 2.5D IC Packaging Market report:

The 3D IC and 2.5D IC Packaging Market is populated by several key players, each contributing to its growth and innovation. Some of the major players include:

The 3D IC and 2.5D IC Packaging Market report is valuable for diverse stakeholders, including:

Essentially, anyone involved in or considering involvement in the 3D IC and 2.5D IC Packaging Market value chain can benefit from the information contained in a comprehensive market report.

Please tell us your area of interest

(Market Segments/ Regions and Countries/ Companies)